CONTROL

Dimitrios Hristu-Varsakelis William S. Levine Editors

Handbook of Networked and Embedded Control Systems

Birkhäuser

# Control Engineering

### Series Editor

William S. Levine Department of Electrical and Computer Engineering University of Maryland College Park, MD 20742-3285 USA

# **Editorial Advisory Board**

Okko Bosgra William Powers

Delft University Ford Motor Company (retired)

The Netherlands US

Graham Goodwin Mark Spong

University of Newcastle University of Illinois Australia Urbana-Champaign

USA

Petar Kokotović

University of California Iori Hashimoto

Santa Barbara Kyoto University

USA Kyoto Japan

Manfred Morari

ETH Zürich Switzerland

# Handbook of Networked and Embedded Control Systems

Dimitrios Hristu-Varsakelis William S. Levine *Editors*

### **Editorial Board**

Rajeev Alur Karl-Erik Årzén John Baillieul Tom Henzinger

Birkhäuser Boston • Basel • Berlin Dimitrios Hristu-Varsakelis Department of Applied Informatics University of Macedonia Thessaloniki, 54006 Greece William S. Levine

Department of Electrical and

Computer Engineering

University of Maryland

College Park, MD 20742

USA

#### Library of Congress Cataloging-in-Publication Data

Handbook of networked and embedded control systems / Dimitrios Hristu-Varsakelis,

William S. Levine, editors.

p. cm. – (Control engineering)

Includes bibliographical references and index.

ISBN 0-8176-3239-5 (alk. paper)

1. Embedded computer systems. I. Hristu-Varsakelis, Dimitrios. II. Levine, W. S. III. Control engineering (Birkhäuser)

TK7895.E42H29 2005 629.8'9-dc22

2005041046

ISBN-10 0-8176-3239-5 ISBN-13 978-0-8176-3239-7 e-BSN 0-8176-4404-0

Printed on acid-free paper.

#### ©2005 Birkhäuser Boston

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Birkhäuser Boston, c/o Springer Science+Business Media Inc., 233 Spring Street, New York, NY, 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed in the United States of America. (JLS/MP)

9 8 7 6 5 4 3 2 1 SPIN 10925324

www.birkhauser.com

# Contents

| Preface 1x                                                                                                       |

|------------------------------------------------------------------------------------------------------------------|

| Part I Fundamentals                                                                                              |

| Fundamentals of Dynamical Systems  William S. Levine                                                             |

| Control of Single-Input Single-Output Systems  Dimitrios Hristu-Varsakelis, William S. Levine                    |

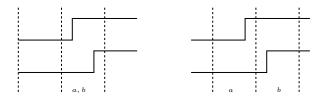

| Basics of Sampling and Quantization  Mohammed S. Santina, Allen R. Stubberud                                     |

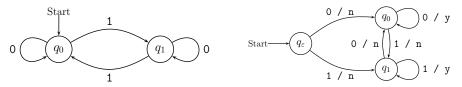

| Discrete-Event Systems Christos G. Cassandras                                                                    |

| Introduction to Hybrid Systems  Michael S. Branicky                                                              |

| Finite Automata         117           M. V. Lawson         117                                                   |

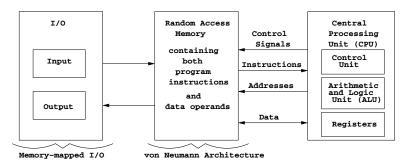

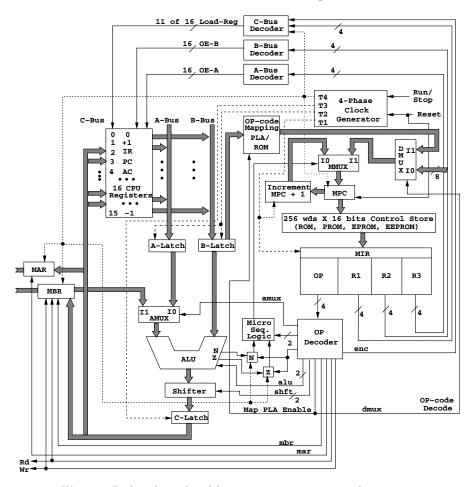

| Basics of Computer Architecture  Charles B. Silio, Jr                                                            |

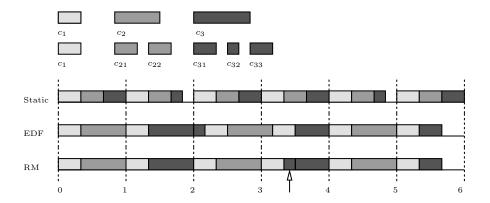

| Real-Time Scheduling for Embedded Systems  Marco Caccamo, Theodore Baker, Alan Burns, Giorgio Buttazzo,  Lui Sha |

| Network Fundamentals  David M. Avelander, Jean Dominique Decetionie. 197                                         |

| Part II Hardware                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basics of Data Acquisition and Control  M. Chidambaram                                                                                                                |

| Programmable Logic Controllers  Gustaf Olsson                                                                                                                         |

| Digital Signal Processors Rainer Leupers, Gerd Ascheid                                                                                                                |

| Microcontrollers Steven F. Barrett, Daniel J. Pack                                                                                                                    |

| SOPCs: Systems on Programmable Chips William M. Hawkins                                                                                                               |

| Part III Software                                                                                                                                                     |

| Fundamentals of RTOS-Based Digital Controller Implementation $Qing Li$                                                                                                |

| Implementation-Aware Embedded Control Systems  Karl-Erik Årzén, Anton Cervin, Dan Henriksson                                                                          |

| From Control Loops to Real-Time Programs  Paul Caspi, Oded Maler                                                                                                      |

| Embedded Real-Time Control via MATLAB, Simulink, and xPC Target  Pieter J. Mosterman, Sameer Prabhu, Andrew Dowd, John Glass, Tom  Erkkinen, John Kluza, Rohit Shenoy |

| LabVIEW Real-Time for Networked/Embedded Control  John Limroth, Jeanne Sullivan Falcon, Dafna Leonard, Jenifer Loy 447                                                |

| Control Loops in RTLinux Victor Yodaiken, Matt Sherer, Edgar Hilton                                                                                                   |

| Part IV Theory                                                                                                                                                        |

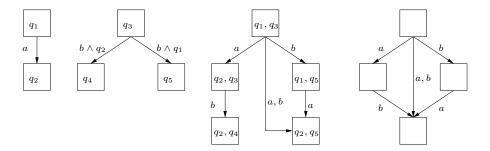

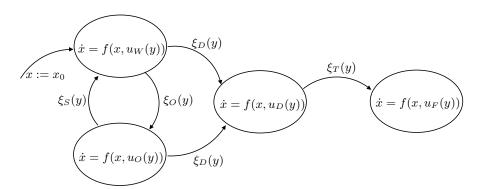

| An Introduction to Hybrid Automata  Jean-François Raskin                                                                                                              |

| An Overview of Hybrid Systems Control  John Lygeros                                                  |

|------------------------------------------------------------------------------------------------------|

| Temporal Logic Model Checking  Edmund Clarke, Ansgar Fehnker, Sumit Kumar Jha, Helmut Veith 539      |

| Switched Systems           Daniel Liberzon                                                           |

| Feedback Control with Communication Constraints  Dimitrios Hristu-Varsakelis                         |

| Networked Control Systems: A Model-Based Approach Luis A. Montestruque and Panos J. Antsaklis        |

| Control Issues in Systems with Loop Delays  Leonid Mirkin, Zalman J. Palmor                          |

| Part V Networking                                                                                    |

| Network Protocols for Networked Control Systems FL. Lian, J. R. Moyne, D. M. Tilbury                 |

| Control Using Feedback over Wireless Ethernet and Bluetooth A. Suri, J. Baillieul, D. V. Raghunathan |

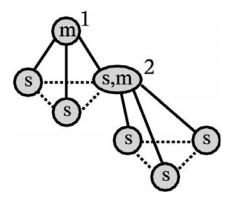

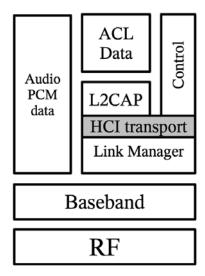

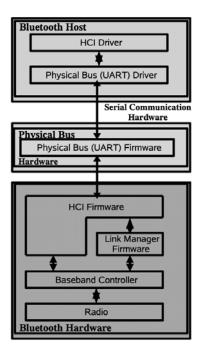

| Bluetooth in Control Bo Bernhardsson, Johan Eker, Joakim Persson                                     |

| Embedded Sensor Networks  John Heidemann, Ramesh Govindan                                            |

| Part VI Applications                                                                                 |

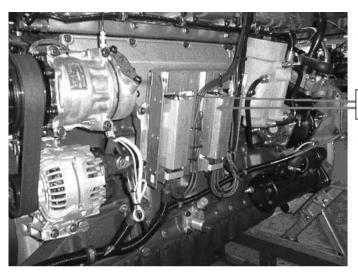

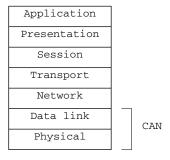

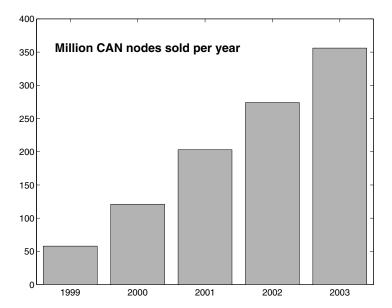

| Vehicle Applications of Controller Area Network Karl Henrik Johansson, Martin Törngren, Lars Nielsen |

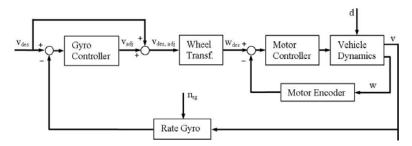

| Control of Autonomous Mobile Robots  Magnus Egerstedt                                                |

| Wireless Control with Bluetooth  Vladimeros Vladimerou, Geir Dullerud                                |

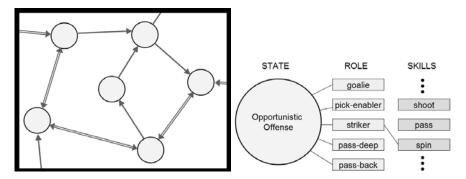

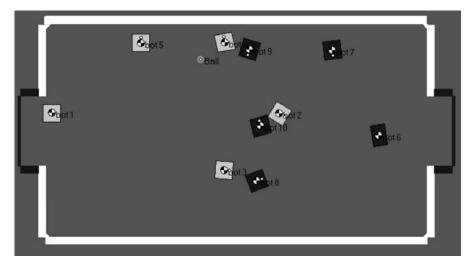

| The Cornell RoboCup Robot Soccer Team: 1999–2003           Raffaello D'Andrea                        |

| Index                                                                                                |

# **Preface**

This handbook was motivated in part by our experience (and that of others) in performing research and in teaching about networked and embedded control systems (NECS) as well as in implementing such systems. Although NECS—along with the technologies that enable them—have become ubiquitous, there are few, if any, sources where a student, researcher, or developer can gain a sufficiently broad view of the subject. Oftentimes, the needed information is scattered in articles, websites, and specification sheets. Such difficulties are perhaps to be expected, given the relative newness of the subject and the diversity of its constitutive disciplines. From control theory and communications, to computer science and electronics, the variety of approaches, tools, and language used by experts in each field often acts as a barrier to understanding how ideas fit within the broader context of networked and embedded control.

With the above in mind, we have gathered a collection of articles that provide at least an introduction to the important results, tools, software, and technologies that shape the area of NECS. Our goal was to present the most important knowledge about NECS in a book that would be useful to anyone who wants to learn about any aspect of the subject. We hope that we have succeeded and that every reader will find valuable information in the book.

We thank the authors of each of the chapters. They are all busy people and we are extremely grateful to them for their outstanding work. We also thank Tom Grasso, Editor, Computational Sciences and Engineering at Birkhäuser Boston, for all his help in developing the handbook, and Regina Gorenshteyn, Assistant Editor, for guiding the editorial and production aspects of the volume. Lastly, we thank Torrey Adams whose copyediting greatly improved the book.

We gratefully acknowledge the support of our wives, Maria K. Hristu and Shirley Johannesen Levine, and our families.

College Park, MD April 2005 Dimitrios Hristu-Varsakelis William S. Levine

**Fundamentals**

# Fundamentals of Dynamical Systems

William S. Levine

Department of ECE, University of Maryland, College Park, MD, 20742, U.S.A. wsl@eng.umd.edu

#### 1 Introduction

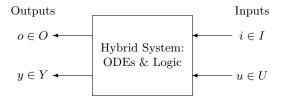

For the purposes of control system design, analysis, test, and repair, the most important part of the very broad subject known as system theory is the theory of dynamical systems. It is difficult to give a precise and sufficiently general definition of a dynamical system for reasons that will become evident from the detailed discussion to follow. All systems that can be described by ordinary differential or difference equations with real coefficients (ODEs) are indubitably dynamical systems. A very important example of a dynamical system that cannot be described by a continuous-time ODE is a pure delay. Most of this chapter will deal with different ways to describe and analyze dynamical systems. We will precisely specify the subclass of such systems for which each description is valid.

The idea of a system involves an approximation to reality. Specifically, a system is a device that accepts an input signal and produces an output signal. It is assumed to do this regardless of the energy or power in the input signal and independent of any other system connected to it. Physical devices do not normally behave this way. The response of a real system, as opposed to that of its mathematical approximation, depends on both the input power and whatever load the output is expected to drive.

Fortunately, the engineers who design real systems generally design them to behave as closely to an abstract system as possible. For electronic devices this amounts to creating subsystems with high input impedance and low output impedance. Such devices require minimal power in their inputs and will deliver the needed power to a broad range of loads without changing their outputs. Where this is not the case it is usually possible to purchase buffer circuits which will drive the load without altering the signal out of the original device. Good examples of this are the circuits used to connect the transistor-transistor logic (TTL) output of a typical microprocessor to a servomotor.

This means that, in both theory and practice, systems can be interconnected without worrying about either the input or output power. It also means

that a system can be completely described by the relation between its inputs and outputs without regard to the ways in which it is interconnected.

## 2 Continuous-Time Systems

We will limit our attention in this section to systems that can be described with sufficient accuracy by ordinary differential equations (ODEs). There are two different ways to describe such systems, in state space form or as an ODE relating the input and the output. In general the state space form is

$$\underline{\dot{x}}(t) = f(\underline{x}(t), \underline{u}(t)) \tag{1}$$

$$y(t) = g(\underline{x}(t), \underline{u}(t)), \tag{2}$$

where  $\underline{\dot{x}}(t)$  denotes the first derivative of the state n-vector  $\underline{x}(t)$ ,  $\underline{u}(t)$  is the m-vector input signal, and  $\underline{y}(t)$  is the p-vector output signal; n,m, and p are integers;  $\underline{f}(\cdot,\cdot)$  is some nonlinear function, as is  $\underline{g}(\cdot,\cdot)$ . The state vector is a complete set of initial conditions for the first-order vector ODE (1). One could be more general and allow both f and g to depend explicitly on time, but we will mostly ignore time-varying systems because of space limitations. We omit precise conditions on f and g needed to insure that there exists a unique solution to (1) for the same reason.

The state space form for a linear time-invariant (LTI) multi-input multi-output (MIMO) system is easily written. It is

$$\underline{\dot{x}}(t) = \underline{Ax}(t) + \underline{Bu}(t) \tag{3}$$

$$\underline{y}(t) = \underline{Cx}(t) + \underline{Du}(t), \tag{4}$$

where the vectors  $\underline{x}$ ,  $\underline{y}$ , and  $\underline{u}$  are column n-, p-, and m-vectors respectively and all the matrices  $\underline{A}$ ,  $\underline{B}$ ,  $\underline{C}$ , and  $\underline{D}$  have the appropriate dimensions. The solution of this exists and is unique for any initial condition  $\underline{x}(0) = \underline{x}_0$  and any input signal  $\underline{u}(t)$ , for all  $0 \le t < t_f$ .

It is worthwhile to be more precise about the meaning of "signal."

**Definition 1.** A scalar continuous-time signal, denoted by  $\{u(t) \text{ for all } t, t_0 \leq t < t_f \}$  is a measurable mapping from an interval of the real numbers into the real numbers.

The requirement that the mapping be measurable is a mathematical technicality that insures, among some more technical properties, that a signal can be integrated. We will generally be more casual and denote a signal simply by u(t). An n-vector-valued signal is just an n-vector of scalar signals. More importantly, we assume that signals over the same time interval can be multiplied by a real scalar and added. That is, if u(t) and v(t) are both signals

defined on the same interval  $t_0 \leq t < t_f$  and  $\alpha$  and  $\beta$  are real numbers, then  $w(t) = \alpha u(t) + \beta v(t)$  is also a signal defined on  $t_0 \leq t < t_f$ . Note that this assumption is true in regard to real signals. Physical devices that will multiply a signal by a real number (amplifiers) and add them (summers) exist. Because of this, it is natural to think of a signal as an element (a vector) in a vector space of signals.

The second ODE description (the first is the state space), in terms of only  $\underline{y}(t)$ ,  $\underline{u}(t)$ , and their derivatives, is difficult to write in a general form. Instead, we show the general LTI single-input single-output (SISO) special case

$$\sum_{i=0}^{n} a_i \frac{d^i}{dt^i} y(t) = \sum_{i=0}^{n} b_i \frac{d^i}{dt^i} u(t), \tag{5}$$

where  $a_i, b_i \in \mathbb{R}$ . Because (5) is unchanged by division by a nonzero real number there is no loss of generality in assuming that  $a_0 = 1$ . Note that it is impossible to have a real physical system for which the highest derivative on the right-hand side n is greater than the highest derivative on the left-hand side.

There are three common descriptions of systems that are only valid for LTI systems, although there is an extension of the Fourier theory to nonlinear systems through Volterra series [1]. We present the SISO versions for simplicity and clarity. One is based on the Laplace transform, although the full power of the theory is not really needed for systems describable by ODEs. There are several versions of the Laplace transform. We use the bilateral or two-sided Laplace transform, defined by

$$Y(s) \stackrel{\text{def}}{=} \int_{-\infty}^{+\infty} y(t)e^{-st}dt, \tag{6}$$

because it is somewhat more convenient and useful for system theory [2]. The unilateral or single-sided Laplace transform is more useful for solving equations such as (5), but we are more interested in system theory than in the explicit solution of ODEs.

We regard the ODE (5) as the fundamental object because for many systems a description of the input-output behavior in terms of an ODE can be derived from the physics. Starting with (5) you need only that the Laplace transform of  $\dot{y}(t) = sY(s)$ , where Y(s) denotes the Laplace transform of y(t) and s is a complex number. Then, taking Laplace transforms of both sides of (5) gives

$$\sum_{0}^{n} a_{i} s^{i} Y(s) = \sum_{0}^{n} b_{i} s^{i} U(s).$$

(7)

Dividing both sides of (7) by U(s) and by  $\sum_{i=0}^{n} a_i s^i$  one obtains

$$\frac{Y(s)}{U(s)} = \frac{\sum_{0}^{n} b_i s^i}{\sum_{0}^{n} a_i s^i} \stackrel{\text{def}}{=} H(s). \tag{8}$$

Notice that H(s), the transfer function of the system, completely describes the relation between the input U(s) and the output Y(s) of the system. It should be obvious that it is easy to go back and forth between H(s) and the ODE in (5) by simply changing s to  $\frac{d}{dt}$  and vice versa.

In fact, the Laplace transform makes it possible to write transfer functions for LTI systems that cannot be precisely described by ODEs. The most important example in control engineering is the system that acts as a pure delay. The transfer function for that LTI system is

$$H(s) = e^{-sT}, (9)$$

where T is the time duration of the delay. However, the pure delay can be approximated to sufficient accuracy by an ODE using the Padé approximation (see "Control Issues in Systems with Loop Delays" by Mirkin and Palmor in this handbook).

Another common description of LTI systems is based on the Fourier transform. The great advantage of the Fourier transform is that, for a large class of real systems, it can be measured directly from the physical system. No mathematics is needed. To prove that this is so, start with either the ODE (5) or the transfer function (8). Let the input  $u(t) = \cos(\omega t)$  for all  $-\infty < t < \infty$ . Using either standard ODE techniques or Laplace transforms—the transient portion of the response is ignored—the solution is found to be

$$y(t) = |H(j\omega)|\cos(\omega t + \angle H(j\omega)), \tag{10}$$

where  $|H(j\omega)|$  denotes the magnitude of the complex number  $H(s=j\omega)$  and  $\angle H(j\omega)$  denotes its phase angle.  $H(j\omega)$  is known as the frequency response of the system.

In the laboratory the input is zero prior to some starting time at which the input  $u(t) = \cos(\omega t)$  for  $t_0 \le t < t_f$  is applied. One then waits until the initial transients die away and then measures the magnitude and phase of the output cosinusoid. This is repeated for a collection of values of  $\omega$  and the gaps in  $\omega$  are interpolated. Note that the presence in the output signal of any distortion or frequency content other than the input frequency indicates that the system is not linear.

One more way to describe an LTI system is based on the system's impulse response. Persisting in our view that the ODE is fundamental, we develop the impulse response by first posing two questions. What is the inverse Fourier transform of  $H(j\omega)$ , where  $H(j\omega)$  is the transfer function of some LTI system? Furthermore, what is the physical meaning of this inverse transform? Note that the identical questions could be asked about the inverse Laplace transform of H(s). The answer to the first question is simply a definition:

$$h(t) \stackrel{\text{def}}{=} \mathcal{F}^{-1}(H(j\omega)) \stackrel{\text{def}}{=} \int_{-\infty}^{\infty} H(j\omega)e^{j\omega t}d\omega/2\pi.$$

(11)

The answer to the second question is much more interesting. Think of the question this way. What input u(t) will produce h(t) as defined in (11)? The

answer is an input that is the inverse Fourier transform of  $U(j\omega) = 1$  for all  $\omega, -\infty < \omega < \infty$ . To see this, just write

$$Y(j\omega) = H(j\omega) \times 1. \tag{12}$$

The required signal is known as the unit impulse or Dirac delta function and is denoted by  $\delta(t)$ . Its precise meaning and interpretation require considerable mathematics and imagination [2,3] although this discussion shows it must be, in some sense, the inverse Fourier transform of 1. In any case, this is why h(t) as defined in (11) is known as the impulse response. It is a complete representation of the LTI system. Knowing the impulse response and the input signal, the output is computed from what is called a convolution integral,

$$y(t) = \int_{-\infty}^{\infty} h(t - \tau)u(\tau)d\tau. \tag{13}$$

Notice that the integral has to be computed for each value of t,  $-\infty < t < \infty$ , making the calculation of y(t) by this means somewhat tedious.

The generalization of the Laplace and Fourier transforms and the impulse response and convolution integral to LTI MIMO systems is easy. One simply applies them term by term to the inputs and outputs. The impulse response can also be used on LTI systems, such as the pure delay of duration T ( $h(t) = \delta(t-T)$ ), that cannot be written as ODEs as well as time-varying linear systems. The state space description also applies to time-varying systems.

For LTI systems that can be described by an ODE of the form (5), the ODE, transfer function H(s), frequency response  $H(j\omega)$ , and impulse response h(t) descriptions are completely equivalent. Knowing any one, you can compute any of the others. Given the state space description (3), it is possible to compute any of the other descriptions. We illustrate by computing  $\underline{H}(s)$ . Taking Laplace transforms of both sides of (3),

$$sX(s) = AX(s) + BU(s) \tag{14}$$

$$(s\underline{I} - \underline{A})\underline{X}(s) = \underline{BU}(s) \tag{15}$$

$$\underline{X}(s) = (s\underline{I} - \underline{A})^{-1}\underline{B}\underline{U}(s) \tag{16}$$

$$\underline{H}(s) = \underline{C}(s\underline{I} - \underline{A})^{-1}\underline{B} + \underline{D}.$$

(17)

The opposite direction, computing an  $\underline{A}$ ,  $\underline{B}$ ,  $\underline{C}$ , and  $\underline{D}$  such that (17) holds given  $\underline{H}(s)$  or its equivalent, is slightly more complicated. Many choices of  $\underline{A}$ ,  $\underline{B}$ ,  $\underline{C}$ , and  $\underline{D}$  will produce the same  $\underline{H}(s)$ . They need not have the same number of states. The state space description is completely equivalent to the other descriptions if and only if it is minimal. The concepts of controllability and observability are needed to give the precise meaning of minimal. This will be discussed at the end of Section 4.

# 3 Discrete-Time Systems

There are exact analogs for discrete-time systems to each of the descriptions of continuous-time systems. The standard notation ignores the actual time completely and regards a discrete-time system as a mapping from an input sequence u[k],  $k_0 \le k \le k_f$  to an output y[k],  $k_0 \le k \le k_f$ , where k is an integer. The discrete-time state space description is then

$$\underline{x}[k+1] = f(\underline{x}[k], \underline{u}[k]) \tag{18}$$

$$y[k] = g(\underline{x}[k], \underline{u}[k]), \tag{19}$$

where  $\underline{x}[k]$  is the state *n*-vector,  $\underline{u}[k]$  is the *m*-vector input signal, and  $\underline{y}[k]$  is the *p*-vector output signal; n, m, and p are integers.

A precise definition of a discrete-time signal is the following.

**Definition 2.** A scalar discrete-time signal, denoted by  $\{u[k] \text{ for all integers } k \text{ such that } k_0 \leq k < k_f\}$  is a mapping from a set of consecutive integers into the real numbers.

As for continuous-time signals, an *n*-vector signal is just an *n*-vector of scalar signals. The same scalar multiplication and addition apply in discrete time as in continuous time so discrete-time signals can also be viewed as vectors in a vector space of signals.

The LTI MIMO version is obviously

$$\underline{x}[k+1] = \underline{Ax}[k] + \underline{Bu}[k] \tag{20}$$

$$\underline{y}[k] = \underline{Cx}[k] + \underline{Du}[k]. \tag{21}$$

The discrete-time analog of the ODE description fortuitously is known as an ordinary difference equation (ODE) or in statistics as an autoregressive moving average (ARMA) model. It has the form, in the SISO case,

$$\sum_{0}^{n} a_{i} y(t-i) = \sum_{0}^{n} b_{i} u(t-i), \tag{22}$$

where  $a_i, b_i \in \mathbb{R}$ .

There is a close analog and relative of the Laplace transform that applies to discrete-time systems. It is known as the Z-transform. As with the Laplace transform, we choose to work with the two-sided version which is, by definition,

$$X(z) \stackrel{\text{def}}{=} \sum_{m=-\infty}^{+\infty} x[m]z^{-m} \tag{23}$$

with z a complex number and x[m],  $-\infty < m < \infty$ .

Similarly, there is a discrete-time Fourier transform. It is defined by the pair of equations

$$X(e^{j\omega}) \stackrel{\text{def}}{=} \sum_{k=-\infty}^{+\infty} x[k]e^{-j\omega k}$$

(24)

$$x[k] = \int_{2\pi} X(e^{j\omega})e^{j\omega k}d\omega/2\pi. \tag{25}$$

Notice that  $X(e^{j\omega})$  is periodic in  $\omega$  of period  $2\pi$ . It is not possible to measure the discrete-time Fourier transform. It is possible to compute it very efficiently. Suppose you have a discrete-time signal that has finite duration—obviously something we could have measured as the output of a physical system:

$$x[k] = \begin{cases} x_k & \text{if } 0 \le k \le k_f - 1; \\ 0 & \text{otherwise.} \end{cases}$$

(26)

It is then possible [2,3] to define a discrete Fourier transform of x[k] consisting of exactly  $k_f$  real numbers which we denote by  $X_f[m]$  (the subscript f for Fourier):

$$X_f[m] = \frac{1}{k_f} \sum_{k=0}^{k_f - 1} x[k] e^{-jm(2\pi/k_f)k}.$$

(27)

Applying the transforms to the ODE produces

$$H(z) = \frac{\sum_{i=0}^{n} b_i z^{-i}}{\sum_{i=0}^{n} a_i z^{-i}}$$

(28)

$$H(e^{j\omega}) = \frac{\sum_{i=0}^{n} b_k e^{-jk\omega}}{\sum_{i=0}^{n} a_k e^{-jk\omega}}.$$

(29)

Lastly, the pulse response is the discrete-time analog of the impulse response of continuous-time systems. There are no real difficulties. The pulse response h[k] is just the output of an LTI system when the input is the discrete-time unit pulse, defined as

$$\delta[k] \stackrel{\text{def}}{=} \begin{cases} 1 & k = 0; \\ 0 & \text{otherwise.} \end{cases}$$

The generalizations and equivalences of these different descriptions of discrete-time systems are exactly the same as those for continuous-time systems, as described at the end of Section 2.

# 4 Properties of Systems

Two of the most important properties of systems are causality and stability. Loosely speaking, a system is causal if its response is completely determined

by its past and present inputs. The present output of a causal system does not depend on its future inputs. A similarly loose description of stability would be that small changes in the input or the initial conditions produce small changes in the output. Making these precise is fairly easy for LTI systems.

**Definition 3.** A continuous-time LTI system is said to be causal if its impulse response h(t) = 0 for all t < 0. A discrete-time LTI system is causal if its pulse response h[k] = 0 for all k < 0.

A more abstract and general definition of causality [4] begins by defining a family of truncator systems,  $P_T$ , defined for all real T by their action on an arbitrary input signal as

$$P_T(u(t)) \stackrel{\text{def}}{=} \begin{cases} u(t) & \text{for } t \le T \\ 0 & \text{for } t > T. \end{cases}$$

(30)

**Definition 4.** A system, denoted by S, is causal if and only if  $P_TS = P_TSP_T$  for all T.

It is useful to distinguish two different forms of stability, although they are equivalent for LTI systems. The definitions are given for continuous-time; simply replace t by k for the discrete-time versions.

**Definition 5.** A system is said to be stable if, with  $\underline{u}(t) = 0$  for all  $t \geq 0$ , given any  $\epsilon > 0$  there exists a  $\delta > 0$  such that  $\|\underline{x}(t)\| < \epsilon$  whenever  $\|\underline{x}_0\| < \delta$ , where  $\|\underline{x}(t)\|$  denotes any norm of  $\underline{x}(t)$ , e.g.,  $\sqrt{\sum_{1}^{n} x_i^2}$ . The system is asymptotically stable if it is stable and  $\|\underline{x}(t)\| \to 0$  as  $t \to 0$ .

**Definition 6.** A system is said to be BIBO stable (BIBO stands for bounded-input bounded-output) if  $\|\underline{y}(t)\| \leq M < \infty$  whenever  $\|\underline{u}(t)\| \leq B < \infty$ , for some real numbers M and B.

Notice that Definition 5 requires a state vector and depends crucially upon it. There are many elaborations of these two relatively simple definitions of stability. Many of these can be found in a textbook by H.K. Khalil [5].

There are several simple ways to determine if an LTI system is stable. Given the impulse (pulse) response, the following theorem applies [4,6,7].

**Theorem 1.** A SISO continuous-time LTI system is BIBO stable if and only if  $\int_{-\infty}^{+\infty} |h(t)| dt \leq M < \infty$  for some M.

Replace the integral by an infinite sum to obtain the SISO discrete-time result. Replace the absolute value by a norm to generalize to the MIMO case.

Given either the ODE or the state space description of a system, causality has to be imposed as an extra condition. Differential and difference equations can generally be solved in either direction. For example, the ODE (5) could be solved for y(0) from knowledge of a complete set of "initial" conditions at

$t_f$  and u(t) for all  $0 \le t < t_f$ . Note that the backwards solution may not be unique in the discrete-time case.

Given either H(z) or H(s) causality is related to stability in an interesting way. A deeper understanding of the theory of transforms is needed here. Consider the two-sided (Laplace)Z-transform of a signal y[k] (y(t)) for all  $-\infty < k,t < +\infty$ . It should be apparent from (23) ((6)) that the infinite sum (integral) may not converge for some values of z (s). For example, let the pulse response of an LTI system be

$$h_c[k] = \begin{cases} 0.9^k, & k \ge 0\\ 0, & \text{otherwise.} \end{cases}$$

Then, using (23)

$$H_c(z) = \sum_{k=0}^{+\infty} (0.9/z)^k.$$

Computing the sum (using the fact that  $\sum_{k=0}^{\infty} a^k = 1/(1-a)$  if |a| < 1) gives

$$H_c(z) = \frac{z}{z - 0.9},$$

provided  $|z| > 0.9.$

Now, let the pulse response be

$$H_{ac}[k] = \begin{cases} -0.9^k, & k < 0\\ 0 & \text{otherwise.} \end{cases}$$

Then

$$H_{ac}(z) = \frac{z}{z - 0.9},$$

provided  $|z| < 0.9.$

Notice that two different pulse responses have the identical Z-transform if one ignores the region of the complex plane in which the infinite sum converges.

The key idea, as illustrated by the example, is that the region of the complex plane in which the Z-transform of a causal LTI system converges is the entire region outside of some circle of finite radius. The corresponding result for the Laplace transform is the region to the right of some vertical line in the complex plane. The next obvious question is: How is the boundary of that region determined?

To answer this question, we first assume for simplicity that H(z) has the form of (28). We multiply numerator and denominator by  $z^n$  so we can work directly with polynomials in z. The denominator polynomial of H(z) is then

$$p(z) = \sum_{i=0}^{n} a_i z^{n-i}.$$

(31)

As an *n*th-order polynomial in the complex number z with real coefficients, p(z) has exactly n roots, i.e., values of z for which p(z) = 0. Simply replace z by s to obtain the corresponding continuous-time result.

**Definition 7.** The poles of a SISO LTI system are the roots of its denominator polynomial.

Note that this definition applies equally well to discrete- and continuoustime systems. For systems described by a transfer function of the form (28) or (8), the impulse, or pulse, response can be computed by first performing a partial fraction expansion of H(z) or H(s). For simplicity, we present the result for the case where  $b_0 = 0$  and all the roots of the denominator polynomial are different—i.e., there are no repeated roots. Under these conditions,

$$H(z) = \frac{\sum_{i=1}^{n} b_i z^{n-i}}{\sum_{i=0}^{n} a_i z^{n-i}} = \sum_{i=1}^{n} A_i / (z - p_i),$$

(32)

where  $p_i$  denotes the *i*th pole of the system and  $A_i$  is the corresponding residue. Note that both  $A_i$  and  $p_i$  could be complex. If they are, then because  $a_i$  and  $b_i$  are real, the system must also have a pole that is the complex conjugate of  $p_i$ , and the residue of this pole must be the complex conjugate of  $A_i$ . Taking the inverse Z-transform of (32) gives

$$h[k] = \mathcal{Z}^{-1}(H(z)) = \sum_{i=1}^{n} A_i / (z - p_i)^i = \begin{cases} \sum_{i=1}^{n} A_i (p_i)^{k-1} & k \ge 1\\ 0 & \text{otherwise.} \end{cases}$$

(33)

Applying Theorem 1 to (33) is the basic step in proving the following theorem.

**Theorem 2.** A discrete-time (continuous-time) LTI system is asymptotically and BIBO stable if and only if all its poles,  $p_i$ , satisfy  $|p_i| < 1$  (Re $(p_i) < 0$ ).

Similarly, the region of convergence of the Z-transform of a causal discretetime LTI system is the region outside a circle of radius equal to  $|p_m|$ , where  $p_m$  is the pole with the largest absolute value. For Laplace transforms, it is the region to the right of  $p_m$ , the pole with the largest  $\text{Re}(p_m)$ .

The numerator polynomial of H(z) or H(s) usually also has roots.

**Definition 8.** The finite zeros of a SISO LTI system are the roots of its numerator polynomial.

The reason for the adjective "finite" is rooted in the appropriate generalization of the definitions of poles and zeros to MIMO LTI systems. It is obvious from the definitions we have given that  $|H(z)| = \infty$  at a pole and that |H(z)| = 0 at a zero of the system. This can be used to give more inclusive definitions of pole and zero. The one for a zero is particularly important.

**Definition 9.** A zero of a SISO LTI discrete-time system is a value of z such that H(z) = 0. Similarly, a zero of a continuous-time SISO LTI system is a value of s such that H(s) = 0.

With this definition of a zero, a system with n poles and m finite zeros can be shown to have exactly n-m zeros at  $\infty$ . The zeros of a system are particularly important in feedback control because the zeros are invariant under feedback. That is, feedback cannot move a zero. Cancelling a zero or a pole is possible, as will be shown in the following section. However, understanding the ramifications of pole/zero cancellation requires at least two more concepts, controllability and observability.

**Definition 10.** A time-invariant system is completely controllable if, given any initial condition  $\underline{x}(0) = \underline{x}_0$  and any final condition  $\underline{x}(T) = \underline{x}_f$ , there exists a bounded piecewise continuous control u(t),  $0 \le t < T$  for some finite T that makes  $\underline{x}(T) = \underline{x}_f$ .

**Definition 11.** A time-invariant system is observable if, given both  $\underline{y}(t)$  and  $\underline{u}(t)$  for all  $0 \le t < T$  for some finite T, it is possible to uniquely determine  $\underline{x}(0)$ .

In both definitions it is assumed that the system is known. In particular, for LTI systems,  $\underline{A}$ ,  $\underline{B}$ ,  $\underline{C}$ , and  $\underline{D}$  are known. There are also simple tests for controllability and observability for LTI systems.

**Theorem 3.** An LTI system is controllable if and only if the  $n \times nm$  matrix  $\underline{C} = [\underline{B} \ \underline{AB} \ \underline{A}^2 \underline{B} \ ... \ \underline{A}^{n-1} \underline{B}]$  has rank n.

**Theorem 4.** An LTI system is observable if and only if the  $pn \times n$  matrix

$$\underline{\mathcal{O}} = \begin{bmatrix} \underline{C} \\ \underline{CA} \\ \underline{CA^2} \\ \vdots \\ CA^{n-1} \end{bmatrix}$$

(34)

$has \ rank \ n.$

As usual, there are many elaborations of the concepts of controllability and observability, providing precise extensions of these ideas to time-varying systems and further clarifying their meaning. Good sources for these more advanced ideas are the books by Kailath and Rugh [6,7].

As mentioned earlier, given  $\underline{H}(s)$  or its equivalent, the problem of finding  $\underline{A}, \underline{B}, \underline{C}$ , and  $\underline{D}$  such that

$$\underline{H}(s) = \underline{C}(s(I) - \underline{A})^{-1}\underline{B} + \underline{D}$$

(35)

has some subtleties. It is known in control theory as the realization problem and is covered in great detail in Kailath [6]. The SISO case is considerably simpler than the MIMO case. For brevity, we denote a state space model by its four matrices, viz.  $\{\underline{A}, \underline{b}, \underline{c}, d\}$ .

**Definition 12.** A realization of a SISO transfer function H(s) is minimal if it has the smallest number of state variables among all realizations of H(s).

**Theorem 5.** A realization,  $\{\underline{A}, \underline{b}, \underline{c}, d\}$ , of H(s) is minimal if and only if  $\{\underline{A}, \underline{b}\}$  is controllable and  $\{\underline{c}, \underline{A}\}$  is observable.

All minimal realizations are equivalent, in the following sense.

**Theorem 6.** Any two minimal realizations are related by a unique  $n \times n$  invertible matrix of real numbers (i.e., a similarity transformation).

The idea behind this theorem is that two n-dimensional state vectors are related by a similarity transformation. Specifically, if  $\underline{x}_1$  and  $\underline{x}_2$  are two n-vectors, then there exists an invertible matrix  $\underline{P}$  such that  $\underline{x}_2 = \underline{P}\underline{x}_1$ . Define  $\underline{x}_2(t) \stackrel{\text{def}}{=} \underline{P}\underline{x}_1(t)$ . Differentiating both sides and making the obvious substitution gives

$$\underline{\dot{x}}_2(t) = \underline{P}\underline{\dot{x}}_1(t) = \underline{P}(\underline{A}\underline{x}_1(t) + \underline{b}\underline{u}(t)). \tag{36}$$

Because  $\underline{P}$  is invertible we can rewrite this as

$$\underline{\dot{x}}_2(t) = \underline{PAP}^{-1}\underline{x}_2(t) + \underline{Pb}u(t). \tag{37}$$

Applying this to the output equation shows that the following two realizations are equivalent in the sense that they have the same state dimension and produce the same transfer function:

$$\{\underline{A}, \underline{b}, \underline{c}, d\} \leftrightarrow \{\underline{PAP}^{-1}, \underline{Pb}, \underline{cP}^{-1}, d\}.$$

(38)

As will be demonstrated in the following section, it is possible to combine an LTI system with a pole at, say  $p_0$ , in series with an LTI system with a zero at the same value,  $p_0$ . The resulting transfer function could, theoretically, be reduced by cancelling the pole/zero pair, i.e., dividing out the common factor. It is not a good idea to perform this cancellation. The following theorem explains the difficulty.

**Theorem 7.** A controllable and observable state space realization of a SISO transfer function H(s) exists if and only if H(s) has no common poles and zeros, i.e., no possible pole/zero cancellations.

Thus, a SISO LTI system that has a pole zero cancellation must have at least one internal pole, i.e., a pole that cannot be seen from the input/output behavior of the system. If one attempts to cancel an unstable pole with a zero, the resulting system will be unstable even though this instability may not be evident from the linear input-output behavior. Generally, the instability will be noticed because it will drive the system out of its linear region.

The idea of pole/zero cancellations is formalized in the following definition.

**Definition 13.** A SISO LTI system is irreducible if there are no pole/zero cancellations in its transfer function.

In the SISO case, any minimal realization of an irreducible LTI system is completely equivalent to any other description of the system. Furthermore, the poles of the system are exactly equal to the eigenvalues of the  $\underline{A}$  from any minimal realization. This allows us to write the following theorem linking all of the properties we have described.

**Theorem 8.** The following statements are equivalent for causal irreducible SISO LTI systems:

- The system is BIBO stable

- The system's minimal realizations are controllable, observable, and asymptotically stable

- If the system is discrete-time, all its poles are inside the unit circle (have real part < 0 if continuous time).

The MIMO generalizations of all of these results, including the definition and interpretation of zeros, and the meaning of irreducibility are vastly more complicated. See Kailath [6] for the details. There is a remarkable generalization of the idea of the zeros of a transfer function to nonlinear systems. An introduction can be found in an article by Isidori and Byrnes [8].

## 5 Interconnecting Systems

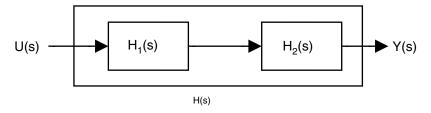

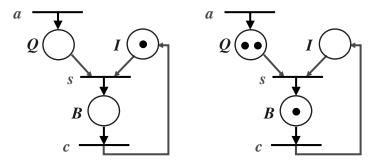

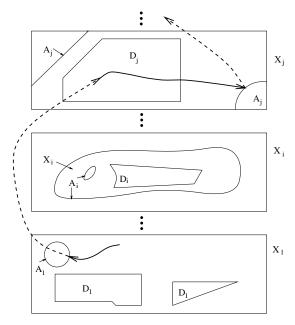

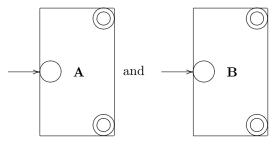

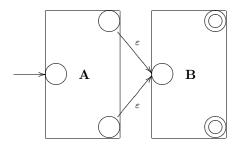

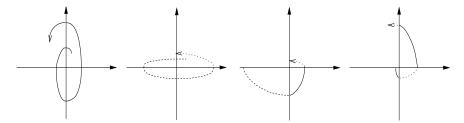

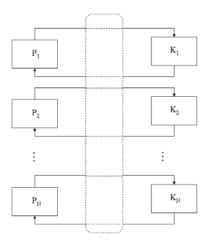

We will describe six ways to interconnect LTI systems in this section. The first three are exactly the same for discrete-time and continuous-time systems. The last three involve the interconnection of continuous-time and discrete-time systems. First, we consider the series connection of two LTI systems as shown in Fig. 1. The result is the transfer function

$$H(s) = H_1(s)H_2(s).$$

(39)

Fig. 1. The series interconnection of LTI systems

A proof is easy:

$$Y(s) = H_2(s)Y_1(s) = H_2(s)H_1(s)U(s).$$

(40)

As mentioned in the previous section, the series connection of an LTI system with a zero at  $p_0$  with an LTI system with a pole at the same value  $p_0$  results in their apparent cancellation in the transfer function, which is completely determined by the input-output behavior of the combined system. Cancellation of stable, well-behaved poles in this way is a common practice in control system design.

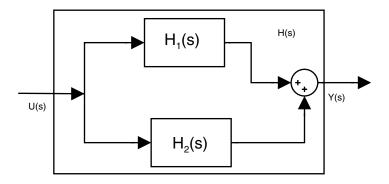

Two LTI systems connected in parallel are shown in Fig. 2. Notice that the figure introduces a new system, known variously as a summer, adder, or comparator. It is completely described by its operation. Its output Y(s) is the sum of its two inputs  $U_1(s) + U_2(s)$ . Thus,

$$Y(s) = Y_1(s) + Y_2(s) = H_1(s)U(s) + H_2(s)U(s) = (H_1(s) + H_2(s))U(s).$$

(41)

Fig. 2. The parallel interconnection of LTI systems

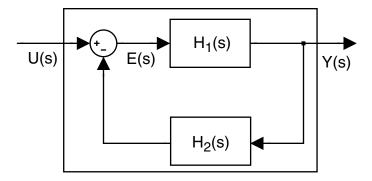

There is another way of combining subsystems, the feedback interconnection, illustrated in Fig. 3. Notice that the transfer function of the combined system is

$$H(s) = \frac{Y(s)}{U(s)} = \frac{H_1(s)}{1 + H_1(s)H_2(s)}.$$

(42)

This result can be derived by recognizing that  $E(s) = U(s) - H_2(s)Y(s)$  and that  $Y(s) = H_1(s)E(s)$ , and doing some arithmetic.

Combining a discrete-time system in series with a continuous-time system requires an appropriate interface. If the output of the continuous-time system is input into the discrete-time system, then a sampler is needed. Conceptually this is simple. If y(t) denotes the output of the continuous-time system and u[k] denotes the input to the discrete-time system, then the sampler makes

Fig. 3. The feedback interconnection of LTI systems

$$u[k] \stackrel{\text{def}}{=} y(kT_s), \tag{43}$$

where  $T_s$  is a fixed time interval known as the sampling interval and (43) holds for all integer k in some set of consecutive integers. Note that we are assuming the sampling interval is constant even though in many applications, especially involving embedded and networked computers, the sampling interval is not constant and can even fluctuate unpredictably. The theory is much simpler when  $T_s$  is constant. In fact  $T_s$  is often constant, and small fluctuations in the sampling interval can often be neglected. Note also that the series combination of a sampler and an LTI system is actually time varying.

One naturally expects sampling to lose information. Remarkably, it is theoretically possible to sample a continuous-time signal and still be able to reconstruct the original signal from its samples exactly, provided the sampling interval  $T_s$  is short enough. The precise details can be found in "Basics of Sampling and Quantization" by Santina and Stubberud in this handbook.

Combining a discrete-time system in series with a continuous-time system in the opposite order requires that the interface convert a discrete-time signal into a continuous-time one. Although there are several ways to do this, the most common and simplest way is to hold the discrete value for the whole sampling interval as shown below,

$$u(t) = y[k]$$

for all  $t$ ,  $kT_s \le t < (k+1)T_s$ . (44)

The last of the six interconnections combines the previous two. It is the feedback interconnection of a discrete-time system with a continuous-time system. The problem is to characterize the combined system in a simple, precise, and convenient way. An exact discrete-time version of the continuous-time system can be obtained as follows. The solution to (3) starting from the initial condition  $\underline{x}(t_0) = \underline{x}_0$  at  $t = t_0$  is

$$\underline{x}(t) = e^{\underline{A}(t-t_0)}\underline{x}_0 + \int_{t_0}^t e^{\underline{A}(t-\tau)}\underline{B}\underline{u}(\tau)d\tau \tag{45}$$

$$y(t) = \underline{Cx}(t) + \underline{Du}(t), \tag{46}$$

where

$$e^{\underline{A}t} \stackrel{\text{def}}{=} \sum_{0}^{\infty} \frac{(\underline{A}t)^n}{n!}.$$

(47)

Applying these results when the initial condition is  $\underline{x}(kT_s) = \underline{x}[k]$  and the input is  $\underline{u}(t) = \underline{u}[k]$  for  $kT_s \leq t < (k+1)T_s$  where  $T_s$  is the sampling interval gives

$$\underline{x}((k+1)T_s) = e^{\underline{A}T_s}\underline{x}[k] + \int_{k(T_s)}^{(k+1)T_s} e^{\underline{A}((k+1)T_s - \tau)} \underline{B}\underline{u}[k]d\tau. \tag{48}$$

Introducing the change of variables  $\sigma = \tau - kT_s$  in the integral, replacing  $\underline{x}((k+1)T_s)$  by  $\underline{x}[k+1]$ , and factoring out the constant  $\underline{B}\underline{u}[k]$  gives

$$\underline{x}[k+1] = e^{\underline{A}T_s}\underline{x}[k] + \int_0^{(T_s} e^{\underline{A}(T_s - \sigma)} d\sigma \underline{B}\underline{u}[k]. \tag{49}$$

Define

$$\underline{\underline{A}}_d \stackrel{\text{def}}{=} e^{\underline{A}T_s} \tag{50}$$

$$\underline{B}_d \stackrel{\text{def}}{=} \int_0^{T_s} e^{\underline{A}(T_s - \sigma)} d\sigma \underline{B} \tag{51}$$

$$\underline{C}_d \stackrel{\text{def}}{=} \underline{C} \tag{52}$$

$$D_d \stackrel{\text{def}}{=} D. \tag{53}$$

Then, we have the discrete-time system in state space form

$$\underline{x}[k+1] = \underline{A}_{d}\underline{x}[k] + \underline{B}_{d}u[k] \tag{54}$$

$$\underline{y}[k] = \underline{C}_d \underline{x}[k] + \underline{D}_d \underline{u}[k]. \tag{55}$$

Taking the Z-transform gives

$$\underline{H}(z) = \underline{C}_d (z\underline{I} - \underline{A}_d)^{-1} \underline{B}_d + \underline{D}_d. \tag{56}$$

Note that this basic approach will give a discrete-time system that is exactly equivalent to the sampled and held continuous-time system at the output sampling instants even if the sampling interval is not constant and is different at the input and the output. Systems of this type are often referred to as "sampled-data systems." See "Control of Single-Input Single-Output Systems" by Hristu and Levine in this handbook for another way to obtain an exact Z-transform for such a system.

There are many approximations to the exact result in (56) in the literature. This is partly for historical reasons. Many continuous-time control systems

were developed before cheap digital controllers became available. A quick and easy way to convert them to digital controllers was by means of a simple approximation to (56). Control and digital signal processing system designers also often use these approximations. The most commonly used and most useful of these is known variously as the trapezoidal method, Tustin's method, or the bilateral transformation. It is given by the following formula:

$$H(z) = H(s = (\frac{2}{T_s} \frac{z-1}{z+1})),$$

(57)

where  $T_s$  is the sampling interval, H(s) is the continuous-time transfer function, and H(z) is its discrete-time equivalent. More details can be found in many places, two of which are the chapter by Santina, Stubberud, and Hostetter [9] and a book by Franklin, Powell, and Workman [10].

#### 6 Conclusion

This chapter is a very brief introduction to a very large subject. To learn more, it would be reasonable to begin with [2,3], which are undergraduate textbooks. The books by Kailath [6], Rugh [7], and Antsaklis and Michel [4] are graduate textbooks on linear systems. The book by Khalil [5] is a graduate text book on nonlinear systems. The Control Handbook [11] contains approximately 80 articles, each of which is a good starting point for learning about some aspect of dynamical systems and their control.

## References

- F. Lamnabhi-Lagarrique. Volterra and Fliess series expansions for nonlinear systems, in *The Control Handbook*, pp. 879–888, CRC Press, Boca Raton, FL, 1995.

- A. V. Oppenheim and A. S. Willsky with S. Hamid Nawab. Signals and Systems, Prentice-Hall, Upper Saddle River, NJ, 2nd edition, 1997.

- B. P. Lathi. *Linear Systems and Signals*, Oxford University Press, New York, 2nd edition, 2005.

- P. J. Antsaklis and A. N. Michel. *Linear Systems*, The McGraw-Hill Companies, New York, 1997.

- H. K. Khalil. Nonlinear Systems, Prentice-Hall, Upper Saddle River, NJ, 3rd edition, 2002.

- T. Kailath. Linear Systems, Prentice-Hall, Upper Saddle River, NJ, 1980.

- W. J. Rugh. Linear System Theory, Prentice-Hall, Upper Saddle River, NJ, 2nd edition, 1995.

- A. Isidori and C. J. Byrnes. Nonlinear zero dynamics, in *The Control Handbook*, pp. 917–923, CRC Press, Boca Raton, FL, 1995.

- M. S. Santina, A. R. Stubberud, and G. H. Hostetter. Discrete-time equivalents to continuous-time systems, in *The Control Handbook* pp. 265–279, CRC Press, Boca Raton, FL, 1995.

- 10. G. F. Franklin, J. D. Powell, and M. Workman. *Digital Control of Dynamic Systems*, Addison-Wesley, San Diego, CA, 3rd edition, 1997.

- 11. W. S. Levine (Editor). *The Control Handbook*, CRC Press, Boca Raton, FL, 1995.

# Control of Single-Input Single-Output Systems\*

Dimitrios Hristu-Varsakelis<sup>1</sup> and William S. Levine<sup>2</sup>

- Department of Applied Informatics, University of Macedonia, Thessaloniki, 54006, Greece dcv@uom.gr

- <sup>2</sup> Electrical and Computer Engineering, University of Maryland, College Park, MD 20742, U.S.A. wsl@umd.edu

#### 1 Introduction

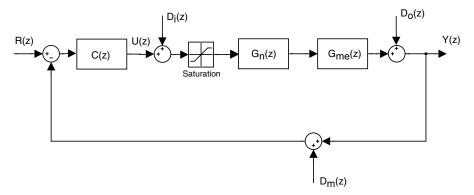

There is an extensive body of theory and practice devoted to the design of feedback controls for linear time-invariant systems. This chapter contains a brief introduction to the subject with emphasis on the design of digital controllers for continuous-time systems. Before we begin it is important to appreciate the limitations of linearity and of feedback. There are situations where it is best not to use feedback in the control of a system. Typically, this is true for systems that do not undergo much perturbation and for which sensors are either unavailable or too inaccurate. There are also limits to what feedback can accomplish. One of the most important examples is the nonlinearity that is present in virtually all systems due to the saturation of the actuator. Saturation will limit the range of useful feedback gains even when instability does not. It is important to keep this in mind when designing controllers for real systems, which are only linear within a limited range of input amplitudes.

The method used to design a controller depends critically on the information available to the designer. We will describe three distinct situations:

- 1. The system to be controlled is available for experiment but the designer cannot obtain a mathematical model of the system.

- 2. The designer has an experimentally determined frequency response of the system but does not have other modeling information.

- 3. The designer has a mathematical model of the system to be controlled.

The second case arises when the underlying physics of the system is poorly understood or when a reasonable mathematical model would be much too complicated to be useful. For example, a typical feedback amplifier might contain 20 or more energy storage elements. A mathematical model for this amplifier would be at least 20th order.

<sup>\*</sup>This work was supported in part by NSF Grant EIA-008001.

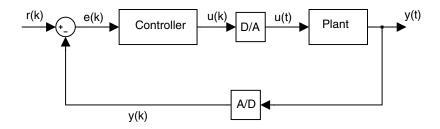

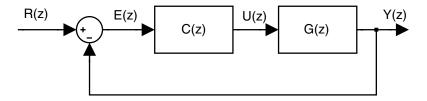

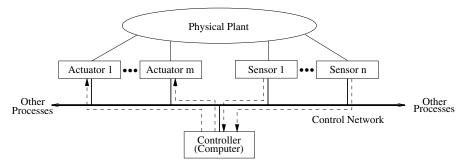

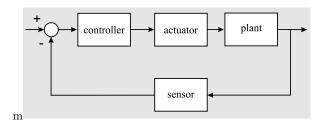

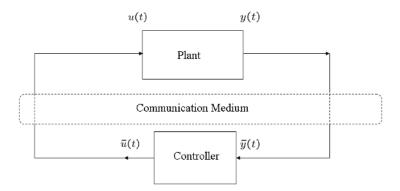

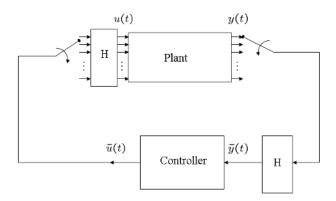

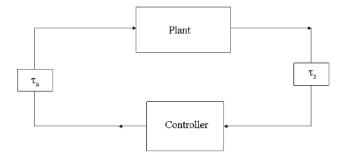

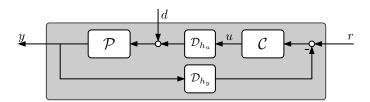

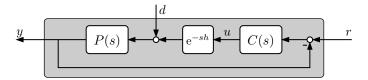

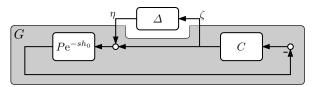

It will be easiest to understand the different design methods if we begin with the third case, where there is an accurate mathematical model of the plant (the system to be controlled). When such a model is available, the feedback control of a single-input single-output (SISO) system begins with the following picture. The plant shown in Fig. 1 typically operates in continuous

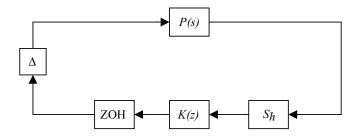

Fig. 1. A sampled-data feedback control system

time. It can be described by its transfer function:

$$Y(s) = G_c(s)U(s),$$

where U(s), Y(s) are the Laplace transforms of the input and output signals respectively, and

$$G_c(s) = \frac{\sum_0^{n-1} b_i s^i}{\sum_0^n a_i s^i} = \frac{\prod_1^{n-1} (s - z_i)}{\prod_1^n (s - p_i)}.$$

(1)

The coefficients  $a_i$ ,  $b_i$  are real; the roots  $z_i$ ,  $p_i$  of the numerator and denominator are the zeros and poles (respectively) of the transfer function. We assume that these parameters are given and that they are constant.

Note that (1) limits the class of systems to those that can be adequately approximated by such a transfer function. For a discussion of controller design when  $G_c(s)$  includes a pure delay, described by  $e^{-sT}$ , see "Control Issues in Systems with Loop Delays" by Mirkin and Palmor in this handbook. The output in Fig. 1 is fed directly back to the summer (comparator). For simplicity and clarity we restrict our discussion to unity feedback systems, as in Fig. 1. It is fairly easy to account for dynamics or filtering associated with the sensor if necessary.

The controller (in cascade with the plant) is to be designed so that the closed-loop system meets a given set of specifications. The controller is assumed to be linear (in a sense to be made precise shortly). Modern controllers are often implemented in a digital computer. This requires the use of analog-to-digital (A/D) and digital-to-analog (D/A) converters in order to interface with the continuous-time plant. This makes the plant, as seen by the

controller, a sampled-data system with input u(k) and output y(k). See the chapter, in this handbook, entitled "Basics of Sampling and Quantization" by Santina and Stubberud for a discussion of the effects of time discretization and D/A and A/D conversion.

# 2 Description of Sampled-Data Systems

The D/A block shown in Fig. 1 converts the discrete-time signal u(k) produced by the controller to a continuous-time piecewise constant signal via a "zero-order hold" (ZOH). Let u(k) be the discrete-time input signal, arriving at the D/A block at multiples of the sampling period T. In the time domain, the ZOH can be modeled as a sum of shifted unit step functions:<sup>3</sup>

$$u(t) = \sum_{0}^{\infty} u(k)[1(t - kT) - 1(t - (k+1)T)].$$

The Laplace transform of the last expression yields

$$U(s) = \underbrace{\sum_{0}^{\infty} u(k)e^{-kTs}}_{U(z)} \left(\frac{1}{s} - \frac{e^{-Ts}}{s}\right).$$

If we think of u(k) as a continuous-time impulse train,  $u(k)\delta(t-kT)$ , then the ZOH has a transfer function

$$G_{ZOH}(s) = \frac{1}{s}(1 - e^{-sT}).$$

From the point of view of the (discrete-time) controller, the transfer function of the sampled-data system is given by the z-transform of the ZOH/plant system

$$G(s) = \frac{1 - e^{-sT}}{s} G_c(s),$$

which is (by  $z = e^{sT}$ )

$$G(z) = \frac{z-1}{z} \mathcal{Z}\{G_c(s)/s\},\,$$

where  $\mathcal{Z}\{G_c(s)/s\}$  is computed by first calculating the inverse Laplace transform of  $G_c(s)/s$  to obtain a continuous-time signal,  $\hat{g}(t)$ , then sampling this signal, and finally computing the Z-transform of this discrete-time signal.

If we let C(z) denote the transfer function of the controller, then the closed-loop transfer function is

<sup>&</sup>lt;sup>3</sup>The unit step function 1(t) equals zero for t < 0, one for  $t \ge 0$ .

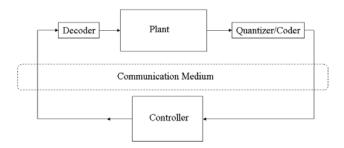

Fig. 2. A sampled-data feedback control system

$$\frac{Y(z)}{U(z)} = G_{cl}(z) = \frac{G(z)C(z)}{1 + G(z)C(z)}.$$

This is illustrated in Fig. 2.

An important point to remember about sampled-data systems is that the real system evolves in continuous time, including the time between the sampling instants. This inter-sample behavior must be accounted for in most applications.

## 3 Control Specifications

The desired performance of the closed-loop system in Fig. 2 is usually described by means of a collection of specifications. They can be organized into four groups:

- Stability

- Steady-state error

- Transient response

- Robustness

These will be discussed in order below.

#### 3.1 Stability

A system is bounded-input bounded-output (BIBO) stable if any bounded input results in a bounded output. A system is internally stable if its state decays to zero when the input is identically zero. If we limit ourselves to linear time-invariant (LTI) systems, then all questions of stability can be settled easily by examining the poles of the closed-loop system. In particular, the closed-loop system is both BIBO and internally stable if and only if all of its poles<sup>4</sup> are inside the unit circle. Mathematically, if the poles of the closed-loop system are denoted by  $p_i$ , i = 1, 2, ..., n then the system is BIBO and internally stable if  $|p_i| < 1$  for all i.

<sup>&</sup>lt;sup>4</sup>This must include any poles that are cancelled by zeros.

#### 3.2 Steady-state error

In many situations the main objective of the closed-loop system is to track a desired input signal closely. For example, a paper-making or metal-rolling machine is expected to produce paper or metal of a specified thickness. Brief, transient errors when the process starts, while undesirable, can often be ignored. On the other hand, persistent tracking errors are a serious problem. Typically, the specification will be that the steady-state error in response to a unit step input must be exactly zero. It is surprisingly easy to meet this requirement in most cases.

The difference between input and output is e(k), or in the z-domain,

$$E(z) = \frac{R(z)}{1 + G(z)C(z)}.$$

We can examine the steady-state error by using the "final value theorem"

$$e(\infty) \stackrel{\triangle}{=} \lim_{k \to \infty} e(k) = \lim_{z \to 1} (1 - z^{-1}) E(z).$$

If the input is a unit step  $(U_s(z) = z/(z-1))$ , then the last equation yields

$$e(\infty) = \lim_{z \to 1} \frac{1}{1 + G(z)C(z)}.$$

(2)

Equation (2) indicates that the steady-state error will be zero provided that

$$\lim_{z \to 1} G(z)C(z) = \infty,$$

which will be true if G(z)C(z) has one or more poles at z=1.

More elaborate steady-state specifications exist, but the details can easily be derived using this example as a model or by consulting the books by Dorf and Bishop [5] or Franklin et al. [6].

#### 3.3 Transient response

The transient response of the closed-loop system is important in many applications. A good example is the stability and control augmentation systems (SCASs) now common in piloted aircraft and some automobiles. These are systems that form an inner (usually multi-input multi-output (MIMO)) control loop that improves the handling qualities of the vehicle. The pilot or driver is the key component in an outer control loop that provides command inputs to the SCAS. The transient characteristics of the vehicle are crucial to the pilot's and driver's handling of the vehicle and to the passenger's perception of the ride. If you doubt this, imagine riding in or driving a car with a large rise time or large percent overshoot (defined below).

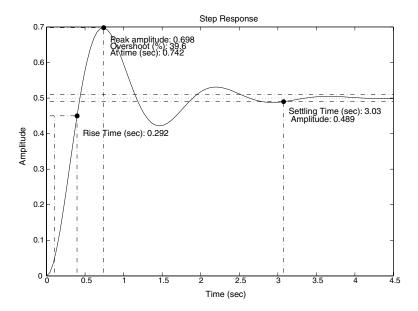

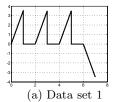

The transient response of an LTI system depends on the input as well as on the initial conditions. The standard specifications assume a unit step as the test input, and the system starts from rest, with zero initial conditions. The resulting step response is then characterized by several of its properties, most notably its rise time, settling time, and percent overshoot. These are displayed in Fig. 3 and defined below.

Fig. 3. The step response of an LTI system and its properties

- Rise time: Usually defined to be the time required for the step response to go from 10% of its final value to 90% of its final value.

- Settling time: Usually defined to be the time at which the step response last crosses the lines at  $\pm 2\%$  of its final value.

- Percent overshoot: Usually defined to be the ratio (peak amplitude minus final value)/(final value) expressed as a percentage.

In each case there are variant definitions. For example, sometimes  $\pm 1\%$  or  $\pm 5\%$  is used instead of  $\pm 2\%$  in the definition of settling time. The final value is the steady-state value of the step response, 0.5 in Fig. 3.

#### 3.4 Robustness

Because a system either is or is not stable, a nominally stable system may become unstable as a result of arbitrarily small differences between the nominal plant G(z) used for design and the real plant. Such differences might be

due to inaccuracies in parameter values, variations in operating conditions, or the deliberate omission of aspects of the nominal plant. For example, the flexure modes of the body and wings of an aircraft are usually omitted from the nominal plant model used for controller design. This underscores the importance of knowing how "close" to instability the closed-loop system is. The "distance to instability" is commonly quantified for SISO LTI systems in two ways. One is the gain margin, namely the gain factor K that must be applied to the forward path (replacing G(z)C(z) by KG(z)C(z) in Fig. 2) in order for the system to become unstable. The other, known as the phase margin, is the maximum amount of delay (or phase shift)  $e^{-j\phi_M}$  that can be introduced in the forward path before the onset of instability.

Robustness, as a specification and property of a controlled system, has received much attention in the research literature in recent years. This has led to robustness tests for MIMO systems as well as a variety of tools for designing robust control systems. See [8,15] for more details.

## 4 Analysis and Design Tools

#### 4.1 The root locus

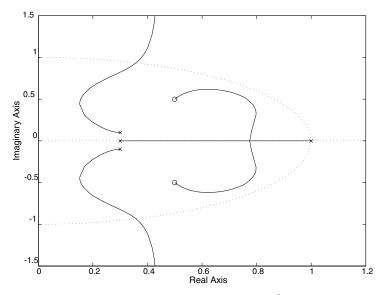

Consider making the controller in Fig. 2 simply a gain, i.e., C(z) = K.

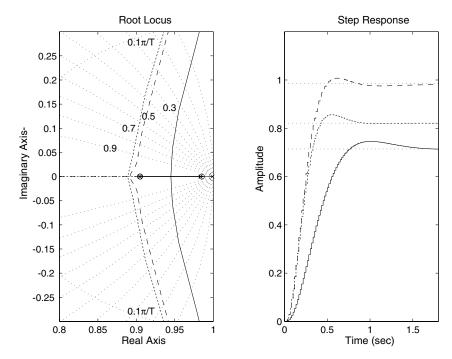

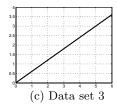

As K varies from 0 to  $\infty$ , the poles of  $G_{cl}(z) = \frac{KG(z)}{1+KG(z)}$  trace a set of curves (called the "root locus") in the complex plane. When K=0 the poles of the "closed-loop system" are identical to the poles of the open-loop system, G(z). Thus, each locus starts at one of the poles of G(z). As  $K \to \infty$  it is possible to prove that the closed-loop poles go to the open-loop zeros, including both the finite and infinite zeros, of G(z). Given a specific value for K, it is easy to compute the resulting closed-loop pole locations. Today, one can easily compute the entire root locus; for example, the MATLAB command rlocus was used to produce Fig. 4. The root locus plot is obviously useful to the designer who plans on using a controller C(z) = K. He or she simply chooses a desirable set of pole locations, consistent with the loci, and determines the corresponding value of K. MATLAB has a command, rlocfind, that facilitates this. Alternatively, one can use the sisotool graphical user interface (GUI) in MATLAB to perform the same task. The choice of pole location is aided by the use of a grid that displays contours of constant natural frequency and damping ratio. We will have more to say regarding the choice of pole locations and the use of the root locus plot in Section 5.1.

By combining the controller and the plant and multiplying by K (the effective plant is then C(z)G(z)), the root locus can be used to determine the gain margin. As will be explained later, the effect of various compensators can also be analyzed and understood by appropriate use of the root locus. Lastly, the idea of the root locus, the graphical display of the pole locations as an implicit function of a single variable in the design, can be very useful in

**Fig. 4.** The root locus when  $G(z) = \frac{z^2 - z + 0.5}{z^4 - 1.9z^3 + 1.18z^2 - 0.31z + 0.03}$

a variety of applications. Modern computers make it fairly easy to generate such root loci.

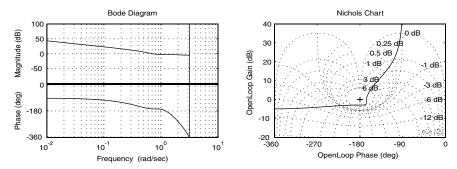

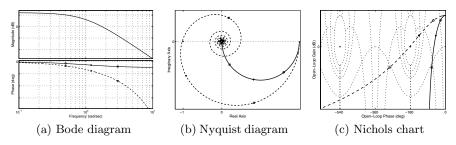

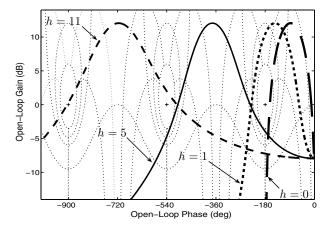

#### 4.2 The Bode, Nyquist, and Nichols plots

There are at least two situations where it is preferable to use the frequency response of the plant rather than its transfer function G(z) for control system design. First, when the plant is either stable or easily stabilized, it is often possible to determine  $|G(e^{j\Omega T})|$  and  $\angle G(e^{j\Omega T})$ , where T is the time interval between samples, experimentally for a range of values of  $\Omega$ . This data is sufficient for control design, completely eliminating the need for an analytical expression for G(z). Second, a system with many poles and zeros can produce a very complicated and confusing root locus. The frequency response plots of such a system can make it easier for the designer to focus on the essentials of the design. This second situation is exemplified by feedback amplifier design, where a state space or transfer function model would be of high order, but the frequency response is relatively simple.

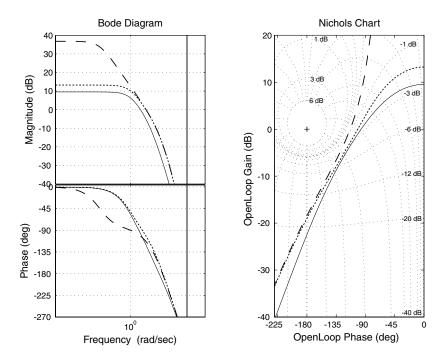

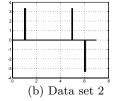

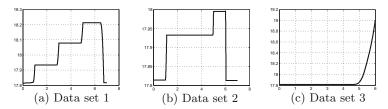

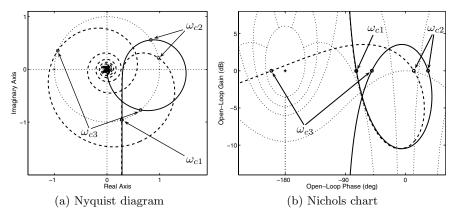

The Nyquist plot of the imaginary part of  $G(e^{j\Omega T})$  versus the real part of  $G(e^{j\Omega T})$  provides a definitive test for stability of the closed-loop system. It also gives the exact gain and phase margins unambiguously. However, it is not particularly easy to use for design. In contrast, both the Bode plots and Nichols chart are very useful for design but can be ambiguous with regard to stability. There are two Bode plots. The Bode magnitude plot presents

$20 \log |G(e^{j\Omega T})|$  on the vertical axis versus  $\log \Omega$  on the horizontal axis. The Bode phase plot shows  $\angle G(e^{j\Omega T})$  on the vertical axis and uses the same horizontal axis as the magnitude plot. The Nichols chart displays  $20 \log |G(e^{j\Omega T})|$  on the vertical axis versus  $\angle G(e^{j\Omega T})$  on the horizontal axis. An example of both plots is shown in Fig. 5. Note that the lightly dotted curves on the Nichols chart are contours of constant gain (in decibels) and phase (in degrees) of the closed-loop system. Thus, any point on the Nichols plot for G(z) also identifies a value of  $20 \log |\frac{G(z)}{(1+G(z))}|$  and of  $\angle \frac{G(z)}{(1+G(z))}$  for some value of  $\Omega$ .

**Fig. 5.** The Bode plots and Nichols chart for  $G(z) = \frac{z^2 - z + 0.5}{z^4 - 1.9z^3 + 1.18z^2 - 0.31z + 0.03}$

The use of logarithmic scaling for the magnitude offers an important convenience: The effect of a series compensator C(z) on the logarithmic magnitude is additive, as is its effect on the phase.

# 5 Classical Design of Control Systems

In reality, the design of a control system usually includes the choosing of sensors, actuators, computer hardware and software, A/D and D/A converters, buffers, and, possibly, other components of the system. In a modern digital controller the code implementing the controller must also be written. In addition, most control systems include a considerable amount of protection against emergencies, overloads, and other exceptional circumstances. Lastly, it is now common to include some collection and storage of maintenance information as well. Although control theory often provides useful guidance to the designer in all of the above-mentioned aspects of the design, it only provides explicit answers for the choice of C(z) in Fig. 2. It is this aspect of control design that is covered here.

#### 5.1 Analytical model-based design

The theory of control design often begins with an explicitly known plant G(z) and a set of specifications for the closed-loop system. The designer is

expected to find a controller C(z) such that the closed-loop system satisfies those specifications. In this case, a natural beginning is to plot the root locus for G(z). If the root locus indicates that the specifications can be met by a controller C(z) = K, then the theoretical design is done. However, it is not a trivial matter to determine from the root locus if there is a value of K for which the specifications are met. Notice that the example specifications in Section 3 include both time domain and frequency domain requirements.

The designer typically needs to be able to visualize the closed-loop step response from knowledge of the closed-loop pole and zero locations only. This is easily done for second-order systems where there is a tight linkage between the pole locations and transient response. Many SISO controlled systems can be adequately approximated by a second-order system even though the actual system is of higher order. For example, there are many systems in which an electric motor controls an inertia. The mechanical time constants in such a system are often several orders of magnitude slower than the electrical ones and dominate the behavior. The electrical transients can be largely ignored in the controller design.

A second-order system can be put in a standard form that only depends on two parameters, the damping ratio  $\zeta$  and the natural frequency  $\omega_n$ . The continuous-time version is

$$G_{cl}(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2},\tag{3}$$

where  $G_{cl}(s)$  denotes the closed-loop transfer function. Notice that the poles of  $G_{cl}(s)$  are located at  $s = -\zeta \omega_n \pm j\omega_n \sqrt{1-\zeta^2} = \omega_n e^{j\pi\pm\cos^{-1}\zeta}$ . For stable systems with a pair of complex conjugate poles,  $0 \le \zeta < 1$ . The description (3) is not used for systems with real poles. The system (3) has step response

$$y(t) = 1 - \frac{e^{-\zeta \omega_n t}}{\sqrt{1 - \zeta^2}} \left( \sin(\sqrt{1 - \zeta^2} \omega_n t + \tan^{-1}(\frac{\sqrt{1 - \zeta^2}}{\zeta})) \right). \tag{4}$$

The constants  $\zeta$  and  $\omega_n$  completely determine the step response. With a little experience a designer can then picture the approximate step response in his or her mind while looking at the pole locations. For a system with additional poles and zeros the actual step response can be quite different from that in (4), but designers need insight and a way to start. An initial design that is very far from meeting the specifications can often be modified and adjusted into a good design after several iterations.

It is possible to create a second-order discrete-time system whose step response exactly matches that of (4). The first step is to choose a time interval between outputs of the discrete-time system, say  $T_s$ . Then, if the continuous-time system has a pole at  $p_i$ , the corresponding discrete-time system must have a corresponding pole at  $p_{id} = e^{p_i T_s}$ . The poles of the continuous-time system (3) are at  $p_i = -\zeta \omega_n \pm j\omega_n \sqrt{1-\zeta^2}$ . Thus, the poles of the discrete-time system are at  $p_{id} = e^{-\zeta \omega_n T_s} e^{\pm j\omega_n \sqrt{1-\zeta^2} T_s}$ . Writing the  $p_{id}$  in polar form

as  $R \cdot e^{j\theta}$  (the subscripts have been dropped because there is only one value) gives

$$R = e^{-\zeta \omega_n T_s} \tag{5}$$

$$\theta = \pm \omega_n \sqrt{1 - \zeta^2} T_s. \tag{6}$$

Solving explicitly for  $\zeta$  and  $\omega_n$  gives

$$\zeta = \pm \frac{\ln(R)}{\sqrt{\theta^2 + (\ln(R))^2}} \tag{7}$$

$$\omega_n = \pm \sqrt{\theta^2 + \left(\ln(R)\right)^2}.$$

(8)

This defines two curves in the z-plane, a curve of constant  $\zeta$  and a curve of constant  $\omega_n$ . These curves can be plotted on the root locus plot—the MAT-LAB command is zgrid. For a second-order system in the standard form (3), both the transient response characteristics and the phase margin are directly related to  $\zeta$  and  $\omega_n$ :

$$rise \ time = t_r \approx \frac{1.8}{\omega_n} \tag{9}$$

settling time =

$$t_s \approx \frac{4.6}{\zeta \omega_n}$$

(10)

$$percent \ overshoot = P.O. = 100 \frac{e^{-\pi\zeta/\sqrt{1-\zeta^2}}}{final \ value}.$$

(11)

The *final value* is the constant steady-state value reached after the transients have died out (*final value* =  $\lim_{k\to\infty} y(k)$ ).

Clearly, if a designer can satisfy the specifications using only C(z) = K, the best value of K can be chosen by plotting the root locus of G(z) and looking at where the loci intersect the contours of constant  $\zeta$  and  $\omega_n$ . If this is not sufficient, there are several standard components one can try to include in C(z) in order to alter the root locus so that its branches pass through the desired values of  $\zeta$  and  $\omega_n$ . The best known of these are the lead and lag compensators defined here for discrete-time systems.

Lead compensator:

$$C_{le}(z) = \frac{\left(\frac{z}{z_l} - 1\right)}{\left(\frac{z}{z_l} - 1\right)}, \quad 0 \le p_l < z_l \le 1$$

(12)

Lag compensator:

$$C_{la}(z) = \frac{(\frac{z}{z_l} - 1)}{(\frac{z}{p_l} - 1)}, \quad 0 \le z_l < p_l \le 1.$$

(13)

Notice that the lead compensator has its zero to the right of its pole and the lag compensator has its zero to the left of its pole.

The principle behind both compensators is the same. Consider the real singularities (poles and zeros) of the open-loop system. Suppose that the rightmost real singularity is a pole. This open-loop real pole will move towards a real open-loop zero placed to its left when the loop is closed with a positive gain K. If the open-loop system has a pole near z=1, it is usually possible to speed up the closed-loop transient response by adding a zero to its left. For several reasons (the most important will be explained in Section 6 on limitations of control) one should never add just a zero. Thus, one must add a real pole to the left of the added zero, thereby creating a lead compensator. This lead compensator will generally improve the transient response. The best value of the gain K can be determined using the root locus plot of the combined plant and lead compensator.

The lag compensator is used to reduce the steady-state error. This is done by adding a real pole near the point z=+1. Adding only a pole will badly slow the closed-loop transient response. Adding a real zero to the left of the pole at z=1 will pull the closed-loop pole to the left for positive gain K, thereby improving the transient response of the closed-loop system.

Another common compensator is the notch filter. It is used when the plant has a pair of lightly damped open-loop poles. These poles can severely limit the range of useful feedback gains, K, because their closed-loop counterparts may become unstable for relatively small values of K. Adding a compensator that has a pair of complex conjugate zeros close to these poles will pull the closed-loop poles towards the zeros as K is increased. One must be careful about the placement of the zeros. If they are placed wrongly, the root locus from the undesirable poles to the added zeros will loop out into the unstable region before returning inside the unit circle. If they are properly placed, this will not happen. Again, one must also add a pair of poles, or the compensator will cause other serious problems, as explained in Section 6.1.

The use of lead and lag compensators is illustrated in the following example.

### Design example